基于Xilinx XC7Z035/45-2FFG676I PL端NVMe Host IP例程设计和使用

一、设计目的

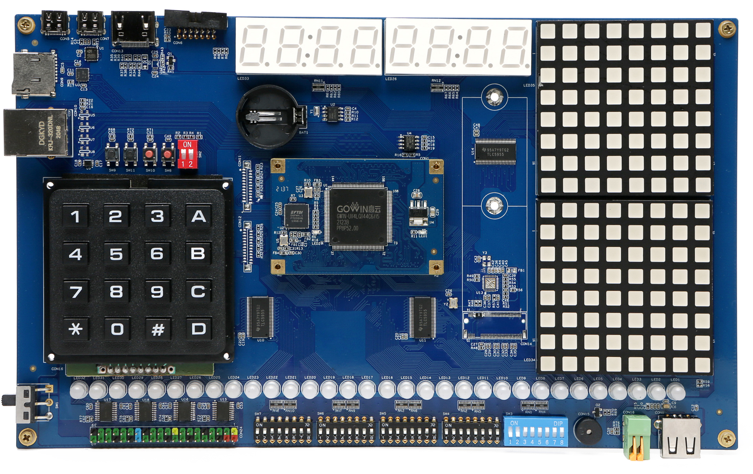

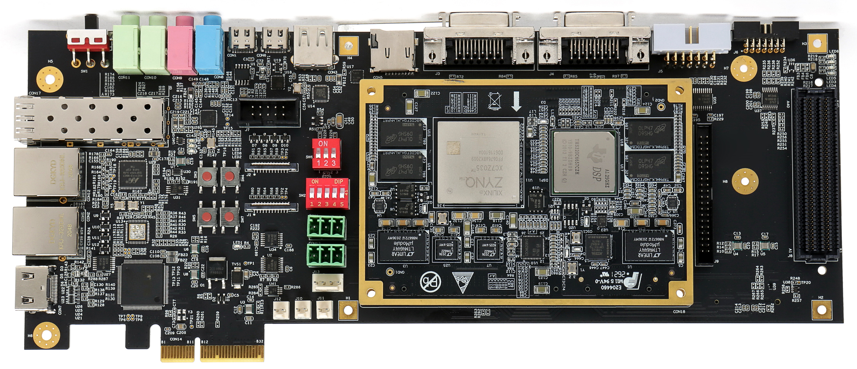

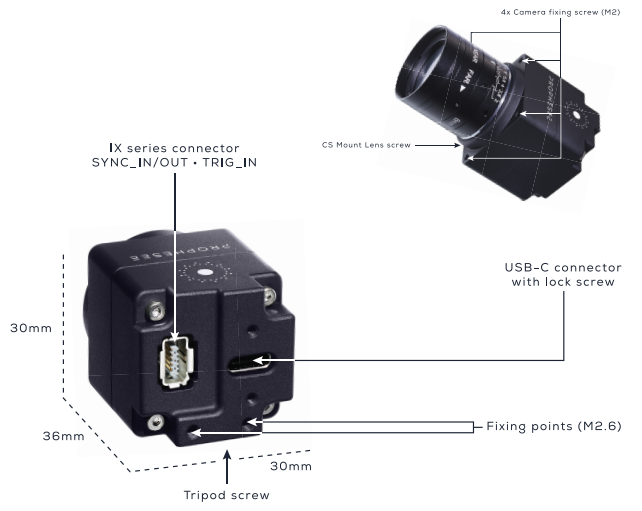

基于广州星嵌电子ZYNQ+DSP评估板XQ6657Z35/45-EVM的Zynq7035/45 PL端实现标准NVMe 1.3协议的Host端,即纯逻辑实现NVMe Host IP。

用户可以根据自身需求,定制NVMe Host FPGA IP,还可以在此基础上定制FPGA纯逻辑来实现文件系统ExFAT。

NVMe Host FPGA IP核使用VHDL硬件描述语言的纯逻辑方式来实现,NVMe物理层使用Xilinx 7系列 PCIe核,无需CPU参与。

目前已在广州星嵌电子ZYNQ+DSP平台上实现并经充分测试验证:

如果使用PCIe 2.0 X2接口,连续读速率:685 MB/s,连续写速率:531 MB/s;

如果使用PCIe2.0 X4接口,连续读速率1277 MB/s,连续写速率1015 MB/s,

日后升级性能还可以提升。

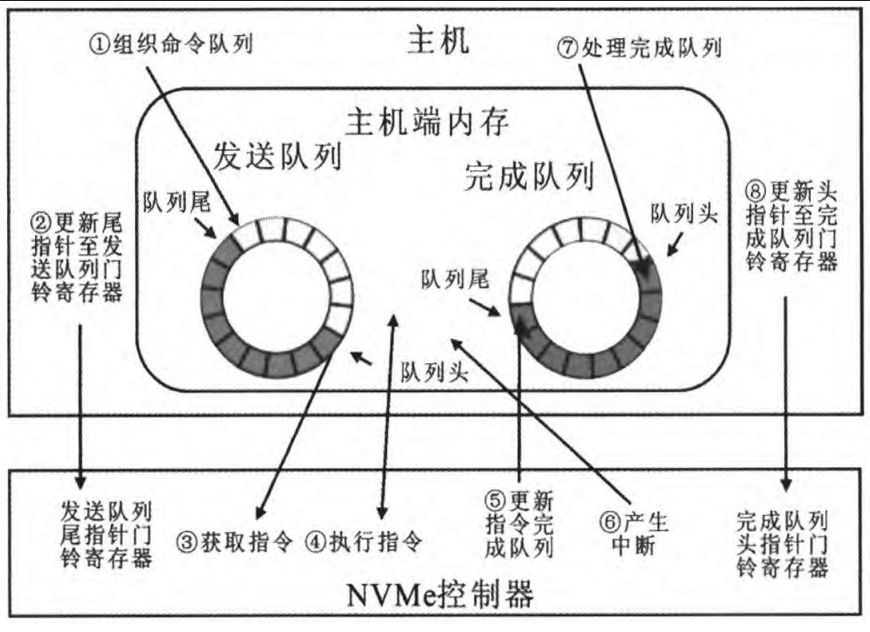

二、NVMe Host FPGA IP核简介

NVMe Host FPGA IP访问接口简单,用户可将此IP当作双端口RAM来使用,只是相对普通双端口RAM而言多增加了一些读、写命令握手接口信号而已。当然,用户还可将IP定制为自身所需要的接口形式。

NVMe Host FPGA IP对外接口图如下:

名词和概念解释:

SLBA(Starting LBA):逻辑块基地址,数据在SSD固态硬盘上的起始地址。

NLB(Number of Logical Blocks):逻辑块数量,指定数据传输大小,需要指出的是这是一个0基数值,即以0为初始值,所以最终传的是(NLB+1)个逻辑块。

NVMe Host FPGA IP支持最大队列数64对,最大队列深度16383,用户可以根据需要进行定制。NVMe Host FPGA IP核源码实现了参数化,可根据用户功能及性能(比如队列数与队列深度)对IP参数进行修改设置。

NVMe Host FPGA IP使用的FPGA 软件开发平台为Vivado 2018.3,用户可以定制为自身所需的FPGA软件开发平台上。

三、资源消耗

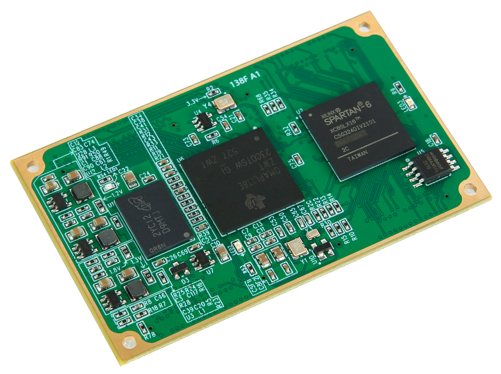

广州星嵌电子ZYNQ+DSP平台上使用ZYNQ 7035/45 PL端作为FPGA开发平台,ZYNQ芯片型号为XC7Z035FFG676-2。NVMe Host FPGA IP在XC7Z035FFG676-2芯片上的资源消耗报表如下:

(注:此为第一版 IP资源消耗图表,还可继续优化)

四、实验平台与测试结果

4.1、NVMe Host FPGA IP测试截图和说明

借助NVMe Host FPGA IP,往NVMe SSD固态硬盘上写入测试数据(例程使用的是累加数),然后读出,并在FPGA上使用逻辑进行比对,并给出比对结果,以验证NVMe硬盘读写数据是否一致。

1、单次写8个扇区

注:NLB = 7,即逻辑块数量8。

数据波形放大查看,可以看到写数据与写地址相同,写数据为累加数:

单次写8个扇区对应的PCIe底层时序波形如下图所示:

2、单次读8个扇区

对上面数据波形放大,可发现读数据与读地址相同,读数据为累加数:

单次读8个扇区对应的PCIe底层时序波形如下图所示:

3、扇区读写比对测试

比对结果如下图高亮信号所示:

Equal_Fail:SSD硬盘读写过程中,只要发现一个数据读写比对不一致,此信号就拉高并一直保持高电平,无论以后数据是否一致,除非复位。

Equal_Valid:读写数据比对结果有效标识,1表示读写对比结果有效。

Equal_Flag:SSD硬盘读写数据一致标识,1表示读写数据一致。

NVMe SSD硬盘读写测试完后,从测试平台上取下NVMe SSD固态硬盘,并将SSD硬盘连接至PC电脑,使用WinHex软件工具分析NVMe SSD固态硬盘的写入数据。

扇区1写入数据:

扇区2写入数据:

扇区3写入数据:

扇区4写入数据:

扇区5写入数据:

扇区6写入数据:

扇区7写入数据:

扇区8写入数据:

4、指定扇区某位置写入指定值

1、指定往SSD硬盘的第1扇区偏移地址127中写入数据0xAA55_ABCD,FPGA VIO设置如下图所示:

2、指定从SSD硬盘的第1扇区偏移地址127中读出数据,读数据为0xAA55_ABCD,与写入数据一致,读时序和读写比对结果如下图所示:

3、从测试平台上取下 NVMe SSD固态硬盘,并将硬盘连接至PC电脑,使用WinHex软件工具分析刚刚写入硬盘的测试数据,如下图所示,也可发现确实已经将0xAA55_ABCD用户数据写入了硬盘:

4.2、NVMe协议相关寄存器读取

1、NVMe协议码:0x010802,对应的PCIe底层读时序波形如下图所示:

2、NVMe协议版本1.3:0x00010300,对应的PCIe底层读时序波形如下图所示:

4.3、NVMe Host IP核支持服务

服务方式 | 配套清单 |

源码 | 源码、使用说明 |

网表不绑定(适用一个系列) | 网表(针对特定FPGA型号,比如XC7Z035FFG676)、使用说明 |

网表绑定 | 网表(网表绑定,绑定FPGA DNA号,也就是绑定FPGA芯片)、使用说明 |

性能指标实测

PCIe接口参数 | NVMe SSD硬盘型号 | 性能指标实测数值 |

PCIe 2.0 X2接口 | 三星NVMe SSD 970 500GB 硬盘 | 连续读速率:685 MB/s; 连续写速率:531 MB/s。 |

PCIe2.0 X4接口 | 三星970 EVO Plus 250GB NVme SSD | 连续读速率:1277 MB/s; 连续写速率:1015 MB/s。 |

上一篇

上一篇